- ELSYS Group

- Overview

- Know-How

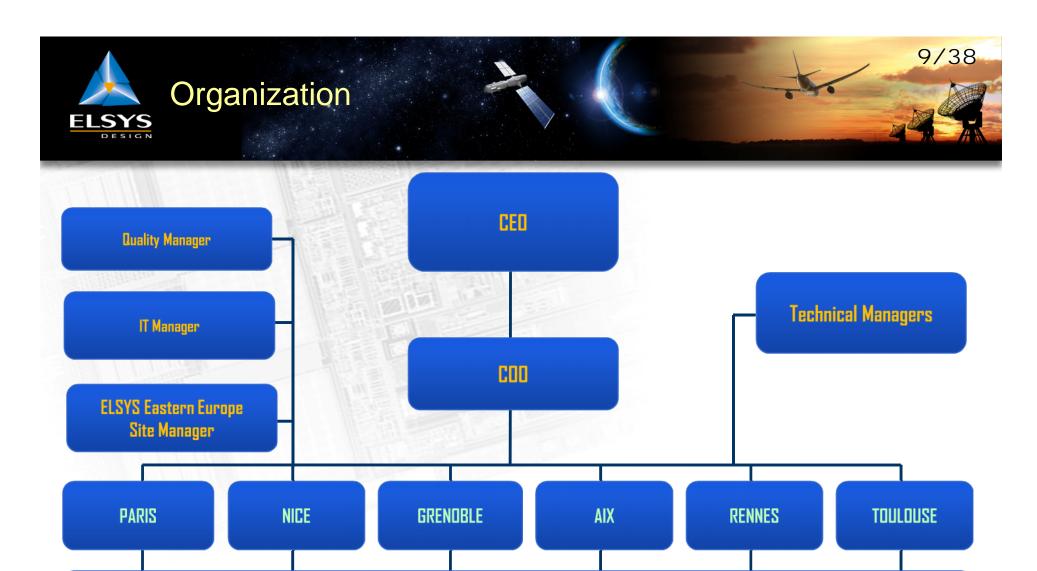

- Organization

- ELSYS Eastern Europe

- Overview

- Know-How

- Organization

- Internship

- Conclusion

Power Line Communications

Applicative Software

Electronics Embedded SW

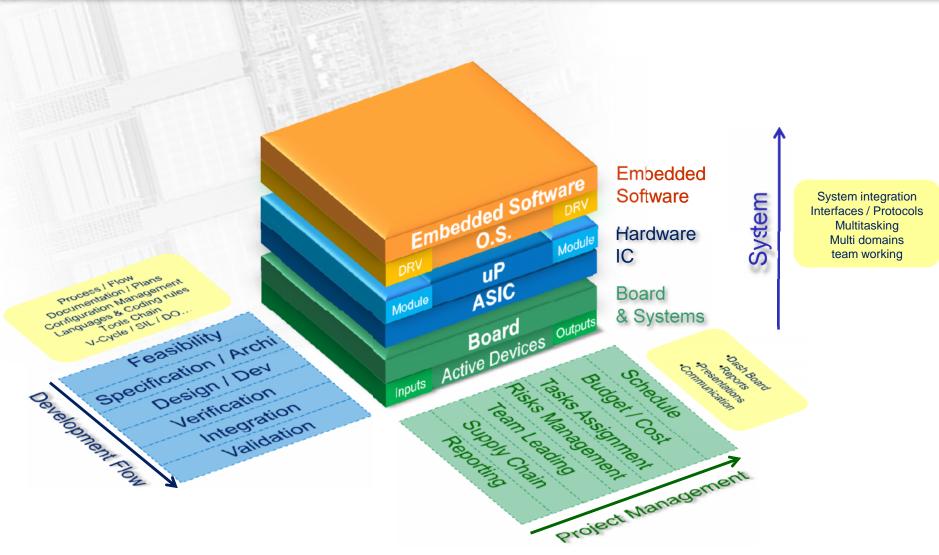

### System Development

Architecture, Hardware, Software

- · Created in 2000

- Independant Capital: 914 K€

- 700 Engineers Turn-Over for 2010: 45 M€

- ISO 9001-2008 Certification

- Tax & Research Accreditation

- Technical Centers:

- 3000 m<sup>2</sup> in France

- 1500 m<sup>2</sup> in Serbia

### **METHODOLOGY**

**Configuration Management**

**Project Management**

**Design Process**

**Quality Assurance**

### Digital IC

- Modelling (SystemC / C / VHDL)

- RTL Design (VHDL / Verilog)

- Verification (TB / Specman / C / SystemVerilog)

- Synthesis / DFT / STA

- Floorplanning / Place & Route

- Verification Back-End

### Analog IC

- Schematics

- Spice / Monte-Carlo Simulations

- Full-Custom Layout

- · Parasitics Extraction

- Physical Verification

FPGA Xilinx / Altera / Actel

ASIC Mentor / Cadence / Synopsys / Magma

Boards: Digital / Analog / RF-HF / Power-Supply

- Schematics

- Spice / Frequencey / Timing Simulations

- Place, Route and Manufacturing Management

- Functional and Environment Validation (EMC, ESD, Climatic...)

Mentor / Cadence - PCAD - ADS - HFSS

### **METHODOLOGY**

**Configuration Management**

\_\_\_\_

**UML Modelling**

**Project Management**

**Development Process**

**Quality Assurance**

### **Signal Processing**

- · Modelling, Simulation

- · Algorithm Implementation

- Optimised Porting on Target

### **Telecom & Network**

- 802.3, X.25, Frame-Relay, HDLC, ATM, SONET/SDH

- GSM, GPRS, EDGE, UMTS, 802.11/Wifi, Bluetooth, ZigBee

- TCP/IP, LON

### **Multimedia**

- Audio: G.711, AMR-NB/WB, AAC, MP3, half-rate, full-rate

- Video: MPEG-1/2/4, H.264

- · System: DVD, DVB

### **Embedded**

- · Firmware, Drivers, BSP

- Autotest

- OS Portting

- Bootloader, Kernel

- Virtualization

#### **Real-Time**

- Multi-task Architectures

- · Critical Software

- RTOS Portting

#### **Industrial**

- · Regulation Software

- GUI / Applicative

- Test Bench (LabView/TS)

### Languages

Matlab, C, C++, ADA, ASM Tcl, Perl, shell

### Processors, DSP, Microcontrellers 8/16/32-bits

Leon, ERC32, ARM, Broadcom, Cypress, Hitachi, Intel, Mitsubishi/Renesas, Motorola/Freescale, NEC, PIC, TI, Siemens, ST-Micro, Toshiba,...

### **Development and DebugTools**

Atmel AVRStudio, Cypress, Freescale CodeWarrior, IAR Workbench, Keil, Lauterbach Trace32, Microsoft Platform Builder et Visual Studio, National Instruments LabView & TestStand, TI Code Composer Studio,...

### **Embedded OS, Real-Time Kernel**

VxWorks, Nucleus, CMX, OS9, eCOS, pSOS, µCOS-II, QNX, WinCE, Linux RT, Linux Embedded, TI DSP/BIOS, Keil RTL-RTX, Mentor Graphics VRTX, OSEK/VDX, LynxOS,...

### **METHODOLOGY**

**Configuration Management**

**UML Modelling**

**Project Management**

**Development Process**

**Quality Assurance**

### **Industrial Software**

- Equipment and Board Management

- Network Management

- Service Industry Software

### **Database**

- Optimisation

- DataWarehouse, ETL

- Reporting

### GUI

- Human Engineering

- Thin & Thick Clients

- Web 2.0 Applications (RIA)

C++, C#.NET, Java et J2EE (EJB, Spring, JSP/Servlet/Struts), Web 2.0, Swing, QT, Open GL ORACLE, mySQL, PostgreSQL, SQL Server

Windows, Linux, Mac OS-X

### **Middleware**

- Interoperability

- Distributed Architecture Web Services, CORBA

### **Protocoles**

- TCP/IP, SNMP, SIP

- SOAP, JSON

- Telecom (PDH, SDH, ATM)

### **Applicative Embedded Software**

- Communication

- Data Process

- Network

• GUI

C/C++, C#.NET Compact Framework, Java-J2ME, QT, OpenGL µLinux, Windows CE, Symbian, MAC OS-X

## **Site Managers**Sales & Technical Managers

Design & Development Engineers

Technical Leaders – Technical Experts

Project Managers

## Technical Referents / Capitalization / Expertise

**Applicative SW**

**Real-Time SW**

**Embedded SW**

Industrialization

Calculator

Test Bench

**Digital Board**

**Analog/Power Board**

ASIC / FPGA

Configuration Management / Quality Process

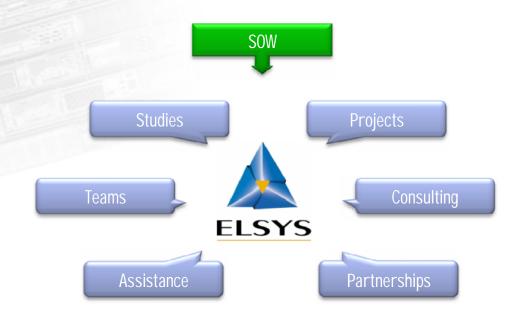

## **Business Model**

## **Business Model**

- Technical Assistance

- Engineering / Expertise / Architecture

- Design / Development

- Methodology

- Fixed-Price Project

- HW Design

- SW Development

- Test Benches

- Customer Partnership

- Dedicated Technical Centers

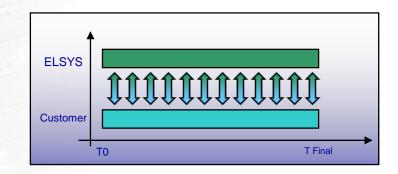

- Technical Assistance (Customer or ELSYS sites)

- The expertise of our consultants as part of client's own task force resources

- Time based fare

- No technical input documentation or device required

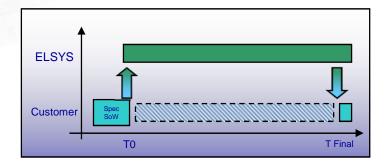

- Fixed Price Projects

- The dedication of our teams working as a 3<sup>rd</sup> part partner / subcontractors

- Quotation based on Specifications and SoW

- Specifications and SoW are mandatory

- IPs and Obsolescence

- Development time saved by purchasing

- ELSYS has dedicated department that can certainly help client solving its obsologous and help client solving its obsolescence issues

6809 Cycle Accurate IP in a PCB with same footprint!

- Created in 2004

- Location: Belgrade Serbia

- Certification ISO 9001-2008 in progress

- The ELSYS' Cost Effective Arm

- Key figures in 2009 / for 2010

- Staff: 70 / 80 engineers

- French Management on Site

- Technical Open Space: 1500 m²

- · Security: camera, badges, guards ...

- VPN secured connection

- 50 m² laboratory

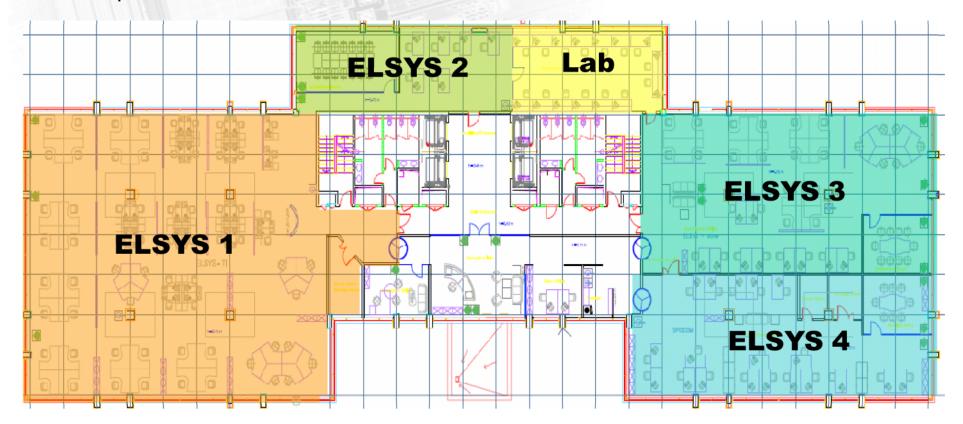

- Space

- 1 entire floor of 1500 m<sup>2</sup> divided in 4 independent entities

- Laboratory

- Floorplan

Offices

- Monitored by the lobby with ID registration.

- CCTV surveillance system and guards 365x7x24.

- Access to our premises:

- Anti-intrusion alarm.

- Access Control System and registration.

- Per each Working Area:

- Access Control System

- Revolving door

- Independent IT network (physically separated)

- IT Security:

- 2 LAN rooms with restricted access.

- All open-space networks can be physically isolated.

- IT policies.

### Integrated Circuits

- Analog / Digital / Mixed Signals / IPs / Obsolescence

- Specification / Architecture / Design /

- Verification / Integration / Validation

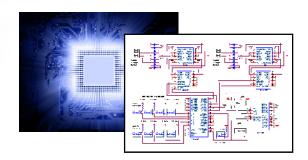

### System and Boards

- Mixed Signals / Power / RF / Obsolescence

- Data processing: DSP, uC, FPGA

- Specification / Architecture / Design

- Integration / Validation / Lab / testbench

### · Embedded Software

- Processors & μC: ARM, PowerPC, DSP, LEON, MC68xxy

- OS: Linux, VxWorks, pSOS

- Kernel, Drivers, Applications, Protocols

- Specification / Architecture / development

- Verification / Integration / Validation

## ELSYS Eastern Europe Background: Board

### **Board & System Design**

- Architecture

- Schematic & Bill of Material

- Place & Route

- Prototyping

- In lab Validation

- Hardware TestBench

- Reference Design

- Documentation (V-Cycle, SIL, DO...)

- Domain: Mixed Signals, Power,

- Data conversion and Processing

- Market: Telecom, Consumer Electronics,

- Transportation

- References: Spidcom Technologies, Alstom

## Mixed Signals Telecommunication Board Design:

→Set Top Box: Internet/Phone VOIP Board design with ARM processors and codec:

- → Specifications

- → System solution

- → Design

- → Layout

- → Protocols implementation

- → Application

- → Prototype

- → Lab test

- → Reference design

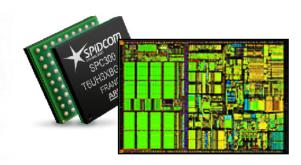

Background: IC

### IC: ASIC / FPGA / SoC

- <u>Design</u> of modules, cells, IPs and uP Cores

- Integration of customized and on-the-shelve components

- Pre-Silicon Verification (VHDL, C, Specman testbench)

- Module / IP Level

- Top Level

- Design For Test

- Layout up to chip finishing

- Post -Silicon Validation + Wake-up phase(Lab, Asm, C)

- Model creation for algorithm verification (Codecs,...)

- Associated **Documentation** (V-Cycle, SIL, DO...)

- Domain: Digital, Analog, Power Management

- <u>Market</u>: Telecom, Consumer Electronics, Transportation, Automatism

- References: Texas Instruments, NXP, IBM, ALSTOM

Example of IC development

Background: Embedded Software

### > Embedded Software

- Processors & uC : ARM, PowerPC, DSP ...

- OS: Linux, VxWorks, pSOS, OSE ...

- Protocols: Bus / Wireless / Network

- Specification / Architecture / Development / Integration / Validation

**ARM:** porting on Linux 2.6, development of low level drivers, applications for telecommunication and networking.

uControler: uCode for Digital Radio Altimeter on Airbus A380 with DO254 norms for THALES.

<u>Protocols:</u> Implementing internet protocols (RTP,HTTP, VOIP, SNMP Agent, IGMP broadcast...). Mobile protocols (low level layer 1: EDGE, GPRS, UMTS)

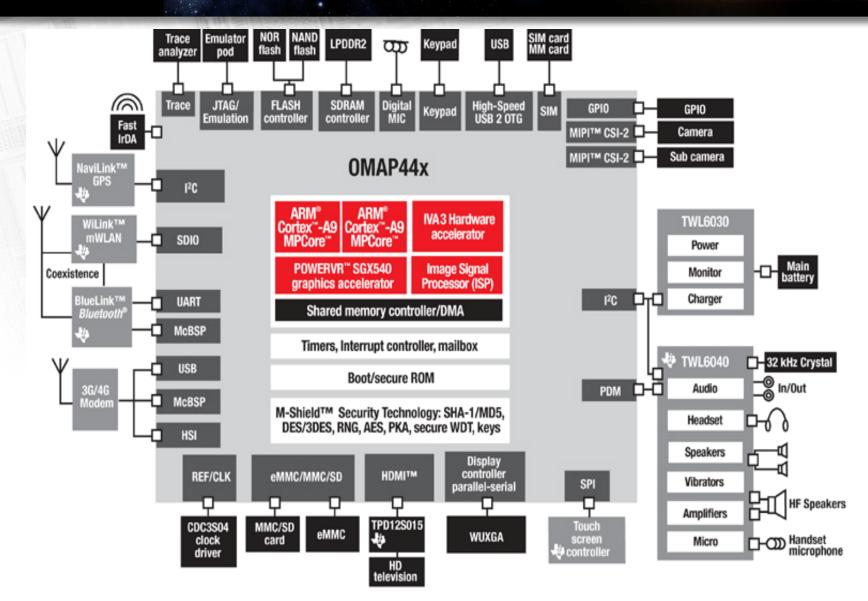

Interfaces: Bus, interfaces and peripherals on OMAP platforms (cameras, keyboard, I2C, USB, memories, ...)

- ELSYS Eastern Europe Developers

- ELSYS Eastern Europe Team Leader

- ELSYS Eastern Europe Developers

- ELSYS Design Team Leader

- ELSYS Eastern Europe Developers

- Customer Team Leader

## ELSYS in Semiconductor Industry

### References

- Texas Instruments

- Analog & Digital IC Design & Validation for Mobile Phones

- Digital IC Design & Validation for Multimedia Platforms

- Analog IC Design, Layout & Validation for Analog/Power Applications

- ST-Ericsson

- Digital & Analog IC Design & Validation for Mobile Phones

- Digital IC Design & Validation for Multimedia Platforms

- Test Chip Design for Automotive Industry

- IBM

- Digital IC Design & Validation for Network Processors

- CPU/GPU Design for Entertainment Industry

- ATMEL

- Digital, Analog & RF IC Design for Medical, Automotive & Biometrics Industries

- EADS Astrium

- Digital IC Design & Validation for Space Industry

- ALCATEL-Lucent

- Digital IC Design for 4G LTE Base-Station

- ARM

- ARM Core Verification

- BULL

- Digital IC Design for Super Computers

- RENESAS

- CPU Design

## Internship in Elsys Eastern Europe

Internship

### > Faculty Projects

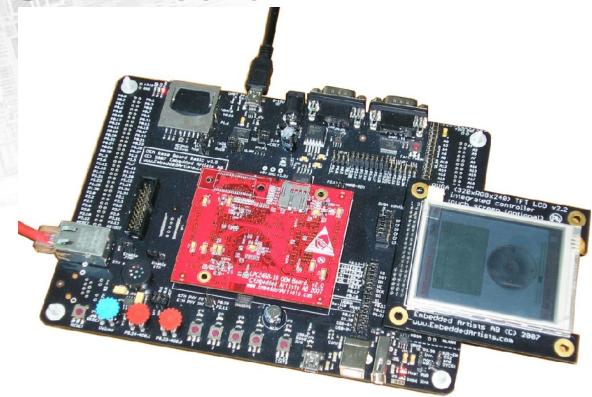

- > ARM7

- > Peripheral drivers

- > Image display via Ethernet

- > USB flash disk

- Music Player

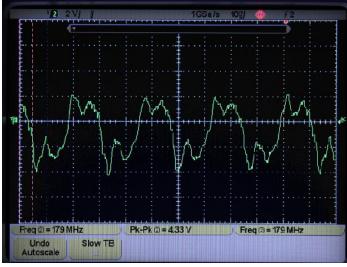

- ➤ Oscilloscope

- > ...

- > SPARTAN 3E

- > VGA controller

- ➤ <u>VIRTEX 4</u>

- > Ethernet Controller

- > VGA Controller

Features & Applications

LPC2468 OEM Board

## > Software Implementations

- Ported uClinux distribution (kernel 2.6.11)

- Implemented drivers for:

- USB

- Ethernet

- LCD Screen

- Touch controller

- USB (Host)

- ADC

- DAC (Sound)

- Keys and Leds

- Network services (FTP,TFTP,NFS)

# 30/38

## > Applications

- Picture viewer (JPG, PIC)

- Sound player (WAV, RAW, MP3)

- Oscilloscope

- Utilization of USB mass storage devices

- LCD driver enhancement

- Touch driver developing (HID interface)

## > SPARTAN 3A FPGA Starter Kit Board

- > Xilinx 700K-gate XC3S700A Spartan-3A FPGA

- Platform Flash PROM, SPI serial Flash PROM, Parallel NOR Flash PROM, DDR2 SDRAM Memory

- > 50MHz On-Board Oscillator, Auxiliary Clock Oscillator Socket, SMA Clock I/O Connector

- > Switches, Buttons, LEDs, 2-line by 16-character LCD

- VGA Display Port, RS-232 Serial Port, PS/2 Mouse/Keyboard Port

- ADC & DAC, 10/100 Ethernet Physical Layer Interface, Stereo Audio Jack

- ➤ Hirose 100-Pin Edge Connector, Differential I/O connectors, Six-Pin Accessory Headers.

## > Application: Implementing VGA Controller

Design moves the image (bitmap format) from Flash to DDR2 SDRAM memory and displays it at 266 Mb/s through the analog VGA output port.

## > Phases of project:

- Programming Flash memory (storing the image to be displayed into the flash)

- Design of DDR2 SDRAM memory interface

- Design of controller that moves image out of the flash memory and into the DDR2 SDRAM memory

- Design of controller that moves data out of the DDR2 SDRAM and into the line buffer (one line of image on demand)

- Designing VGA signal timing to drive the VGA monitor in 640 by 480 pixel mode at 60Hz.

## > ML403 Board - MRTEX 4

- Virtex-4 FX FPGA chip speed grade 12

- > 64 MB of DDR SDRAM

- > Stereo AC97 Audio Codec

- > RS-232 Serial Port

- > 16-Character X 2-Line LCD

- > VGA Output

- > PS/2 Mouse and Keyboard Ports

- > JTAG Configuration Port

- > 10/100/1000 Tri-Speed Ethernet PHY

- ➤ USB Controller with Host and Peripheral ports

## > Application 1: Ethernet Controller

- > GOAL 1 Gbit Ethernet Controller, for usage by various wrappers

- ➤ Used resources Embedded MAC resource in Virtex 4 FPGA, 4 FIFO Memory blocks and controlling logic.

- Each of Receiver and Transmitter has 2 FIFO blocks, one of which is used as a memory for actual frame and the other is used to memorize length of corresponding frame, and in the case of Receiver validity of frame.

- ➤ Interface to On-board PHY chip is GMI

- Also the design is combined with a VGA controller and a decoding logic, to allow change of image being displayed on monitor, depending on the content of length/type field of sent ethernet frame.

## > Application 2: VGA Controller

- > Displaying image stored in on-board DDR SDRAM memory

- Design can be divided on three parts:

- > CRT (VGA connector) interface

- > Memory interface for DDR SDRAM memory

- > FIFO memory makes bridge between these two parts which work in different dock domains

- > This could be used as a module in designs with display.

## > Projects applications...

- Working for World Class Companies

- French Management Work Organization

- · Career Path

- Work Environment

- Trainings and seminars

- · On site employment

- Language courses + Sports

- Colleagues

- Solidarity

- Stability

### **Job Positions:**

ELSYS forecast new positions in 2011 in the following domains:

- Analog Design → analog.job@elsys-eastern.com

- Digital Design → <u>digital.job@elsys-eastern.com</u>

- Embedded Software soft.job@elsys-eastern.com

- Board Design: → board.job@elsys-eatern.com

## Internships:

Like every summer ELSYS will have new internship positions:

- Subjects post at the faculty → April/May 2011

- Applications → until June-15, 2011

- Internship period → July to September 2011

www.elsys-eastern.com